OK01 Opening Keynote "It’s Time to Futureproof our Prosperity by Superfueling Innovation, Enabling Next-Gen AI"

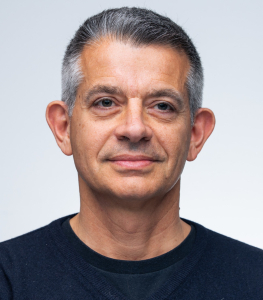

Luc Van den hove, imec, Belgium

The AI field is evolving at an incredibly fast pace, with major models and updates being released almost every month. As these models evolve beyond Large Language Models towards next-gen AI with advanced reasoning capabilities, compute systems struggle to handle the heterogeneous workloads in a performant and sustainable way. However, developing new, AI-optimised compute architectures and the enabling semiconductor technologies takes much more time than writing algorithms. To prevent bottlenecks slowing down AI-based advancements, we must reinvent compute architectures and semiconductor technology platforms.

The presentation will shed light on the need for flexible, versatile compute architectures implemented in flexible, versatile technology platforms while addressing the increasing challenges of density, power and memory. To speed up both advanced semiconductor technology R&D and full stack innovation for future AI applications, imec is expanding its pilot line infrastructure under the EU Chips Act. Next to new infrastructure, imec aims to boost innovation through intensified collaborations with complementary knowledge partners and through further internationalisation, attracting global talent and building strong, local ecosystems for diverse application domains, like health and automotive.

Transformative innovations for humankind hinge on the innovation pace of the semiconductor industry. It’s time to supercharge our innovation engine, it’s time to futureproof our prosperity.